AMD的CPU要学苹果了?还好不是消费级

更新时间:2023-02-23 12:32:29作者:cblsl

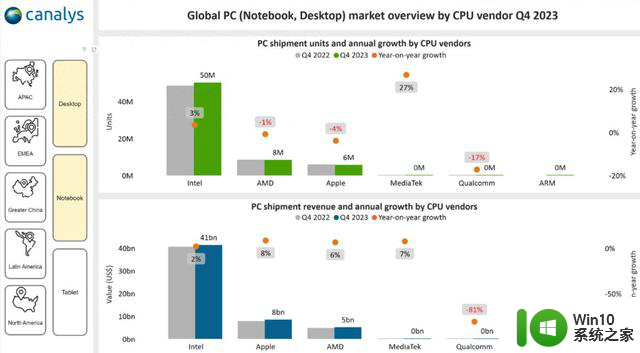

苹果的M系列芯片将内存整合在了CPU上,彻底断了消费者自己加内存的念想。现在不止苹果有这个心思,AMD也提出了类似的集成封装方案。

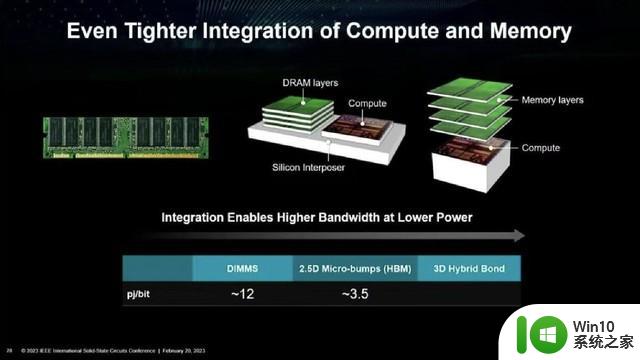

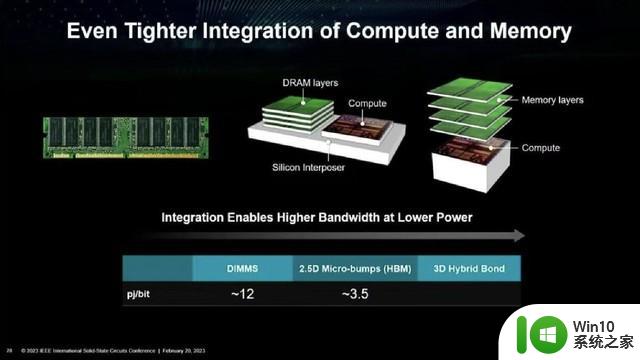

在ISSCC 2023国际固态电路大会上,AMD提出了多种新的集成封装思路。其中一种就是将DRAM内存直接堆叠在CPU处理器内部,而且是多层的,如果堆叠内存容量足够大,甚至可以省去主板上的DIMM插槽,让系统的集成度更高。

关于内存的封装方式,一种是将CPU计算模块和DRAM内存模块并排封装在硅片转接板上。另一种方式是将内存模块直接堆叠在计算模块上方,有点像手机的SoC。AMD表示这种设计允许计算核心以更短的距离、更高的带宽和更低的延迟访问内存,并可以大大降低功耗。2.5D封装可以实现独立存储器30%左右的功耗,3D混合绑定封装只有传统的1/6。

(8125706)